As the integrated circuit (IC) technology advances into smaller nanometre feature sizes, a fixed-error noise known as device mismatch is introduced owing to the dissimilarity between transistors, and this degrades the accuracy of analog circuits. We present an analog co-processor that uses this fixed-pattern noise to its advantage to perform complex computa- tion. This circuit is an extension of our previously published train- able analogue block (TAB) framework and uses multiple inputs that substantially increase functionality. We present measure- ment results of our two-input analogue co-processor built using a 130-nm process technology and show its learning capabilities for regression and classification tasks. We also show that the co-processor, comprised of 100 neurons, is a low-power system with a power dissipation of only 1.1μW. The IC fabrication process contributes to randomness and variability in ICs, and we show that random device mismatch is favorable for the learning capability of our system as it causes variability among the neuronal tuning curves. The low-power capability of our framework makes it suitable for use in various battery-powered applications ranging from biomedical to military as a front-end analog co-processor

Faculty: Chetan Singh Thakur, ESE

Publication: Thakur, C. S., Wang, R., Hamilton, T. J., Tapson, J., R. Etienne-Cummings & van Schaik, A. (2017). An Analogue Neuromorphic Co-processor that Utilises Device Mismatch for Learning Applications. IEEE Transactions on Circuits and Systems I (TCAS-I)

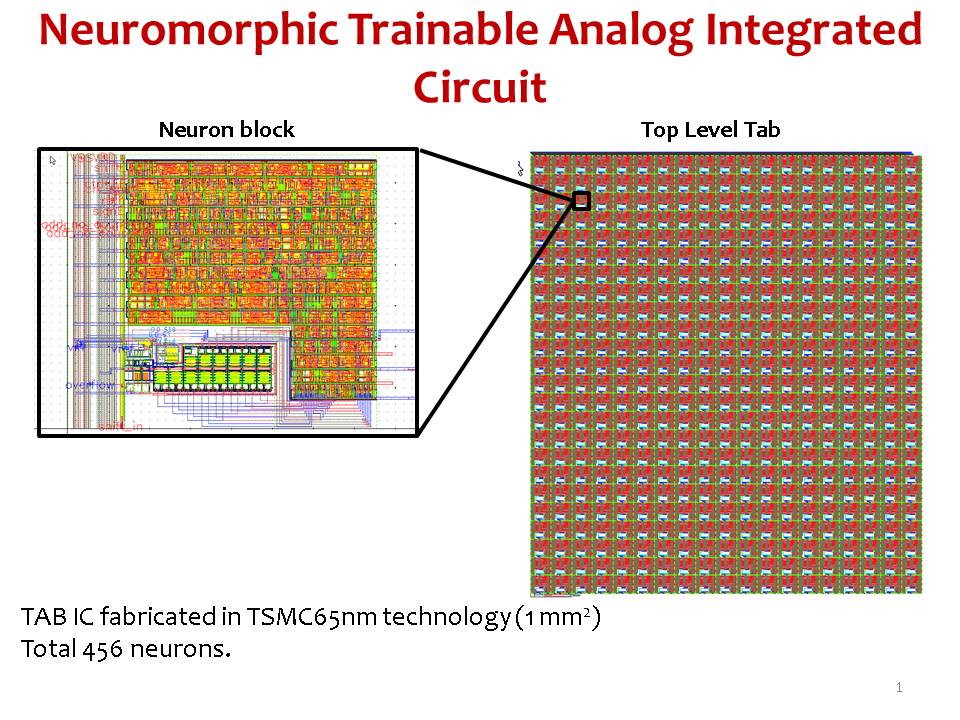

Patent: Thakur, C. S., Hamilton, T. J., Tapson, J., & van Schaik, A. (2014) A Neuromorphic Trainable Analog Block. International PCT. Patent number AU2014904154/WO2016058055